# Design of Q-IDEN D Flip-Flop Using RS-latch

Sangmi Shim<sup>1</sup>, Gisoo Na<sup>2</sup>, Seungwoo Park<sup>1</sup> and Seunghong Hong<sup>1</sup>

<sup>1</sup> School of Electronic Engineering, Inha University Incheon, <sup>2</sup> Department of Electronics Engineering, catholic University of Korea

#### Summary

In this study we design quaternary acting Q-IDEN D flip-flop circuit. First of all, we design thermometer code output circuit, EXOR gate, bias inverter, transmission gate, and binary D flip-flop circuit. Using thermometer code output circuit, EXOR gate, and bias inverter we design multi-valued identity logic circuit, and with multi-valued identity logic circuit and binary D flip-flop we design Q-IDEN and D flip-flop.

Key words:

Quaternary, D-FF, Bias inverters, Transmission gates

# Introduction

From Although developing multi-valued device using voltage mode sometimes causes unpredictable output due to transmission time delay, it has the advantage of easy applicability to particular system and less power consumption. When using voltage mode producing the element, which has multiple threshold voltage and is essential for actualizing multi-valued device, was a really difficult problem. But the appearance of Neuron-MOSFETs enabled actualizing multi-valued systems using general voltage mode CMOS technique.

The advantage of multi-valued circuits using Neuron-MOS NMIN, NMAX circuit is that it can be applied in every multi-valued logic value without changing the structure. But the disadvantage of it was long transmission time and large power consumption.

Neuron-MOS which had the similar characteristic with the neuron of human nerve system was suggested by T. Shibata [1] on the early 1990s, and was typically used in the circuit for forming the intelligent network. These Neuron-MOS can be made by adding several input gates and floating gates to the existing MOSFET structure.

K. W. Current [2] suggested voltage mode quaternary CMOS latch circuit using binary CMOS RS latch circuit acting on single threshold voltage.

T. Uemura et al. suggested tertiary D flip-flop circuit using multi-junction surface tunnel transistor and MOSFET, designed tertiary logic gate using voltage mode CMOS technique, and suggested tertiary flip-flop[3].

M. Inaba [4] et al. suggested quantizer flip-flop and multivalued flip-flop, in other words, analog flip-flop using Neuron-MOS CMOS NMIN circuit. Every element used Neuron-MOS and T-gate circuit was designed using CMOS.

In this study we suggested and designed Q-IDEN D flipflop. Suggested Q-IDEN D flip-flop was designed using Neuron-MOS and occasionally general MOSFET when necessary.

## 2. Component circuits

## 2.1 Bias inverter circuit

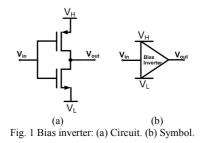

Bias inverter has the same structure with typical binary inverter but uses the bias power supply  $V_H$  and  $V_L$  of a specific value instead of  $V_{DD}$  and GND. Figure 1 shows the circuit diagram and circuit symbol of bias inverter.

The threshold voltage of bias inverter is determined by the bias voltage  $V_{\rm H}$  and  $V_{\rm L}$  as Formula (1) and  $V_{\rm out}$  is determined as Formula (2).

$$V_{TH} = \frac{V_H + V_L}{2} \tag{1}$$

Manuscript received September 5, 2006.

Manuscript revised September 25, 2006.

$$V_{out} = \begin{cases} V_L & V_{in} > V_{TH} \\ V_H & V_{in} < V_{TH} \end{cases}$$

(2)

Bias inverter works in a same mechanism with typical binary inverter. Bias inverter yields low bias voltage  $V_L$  as the output when input voltage  $V_{in}$  is higher than the threshold voltage  $V_{TH}$ , and yields high bias voltage  $V_H$  when  $V_{in}$  is lower than  $V_{TH}$ . Bias voltage  $V_H$  and  $V_L$  has quaternary value, and when the difference of the two values becomes an even number threshold voltage  $V_{TH}$  can't have the middle value (0.5, 1.5, 2.5) of the quaternary level. Table 1 shows the quaternary truth table of bias inverter and Figure 2 shows the result waveform of the simulation experiment of bias inverter. It is verified that the result waveform of the simulation experiment of bias inverter is exactly identical to the quaternary truth table of bias inverter.

Table 1: Quaternary truth table of bias inverter

|                                                      | $V_{H}$                  | $V_L$            | $\dot{V_{TH}}$ | BIA | .S_I | NV | _IN        | BIA   | S_IN | IV_ | OUT |   |

|------------------------------------------------------|--------------------------|------------------|----------------|-----|------|----|------------|-------|------|-----|-----|---|

|                                                      | 3                        | 2                | 2.5            | 3   | 2    | 1  | 0          | 2     | 3    | 3   | 3   |   |

|                                                      | 3                        | 0                | 1.5            | 3   | 2    | 1  | 0          | 0     | 0    | 3   | 3   |   |

|                                                      | 2                        | 1                | 1.5            | 3   | 2    | 1  | 0          | 1     | 1    | 2   | 2   |   |

|                                                      | 1                        | 0                | 0.5            | 3   | 2    | 1  | 0          | 0     | 0    | 0   | 1   |   |

|                                                      |                          |                  |                |     |      |    |            |       |      |     |     |   |

| fave List.                                           | -                        |                  |                |     |      |    | +bias inve | erter |      |     |     |   |

| 0tr0.v(bh)<br>0tr0.v(bl)<br>0tr0.v(bl)<br>0tr0.v(bl) | 0in)                     | 3 -              | × M            |     |      |    |            |       |      |     |     |   |

| OtrOx(inv_                                           | 20 (j)<br>Voltages (jin) | 2 .              |                |     |      |    |            |       |      |     |     |   |

|                                                      |                          | 2                | *              |     |      |    |            |       |      |     |     |   |

|                                                      | Votages (lin)            | 1.               | 10             |     |      |    |            |       |      | _   |     |   |

|                                                      | 10/                      | 0                |                |     |      |    |            |       |      |     |     |   |

|                                                      | (III)                    | 352              | ×              | _   |      |    |            |       | _    |     |     |   |

|                                                      | 100                      | 1,5<br>1<br>500m | RW             |     |      |    |            |       |      |     |     |   |

|                                                      |                          |                  |                |     |      |    |            | -     |      |     |     |   |

|                                                      | Oftages (Iin)            | 2-               | ×              |     |      | 1  |            |       |      | 7   |     | _ |

Fig. 2 Quaternary input and output waves of bias-inverter.

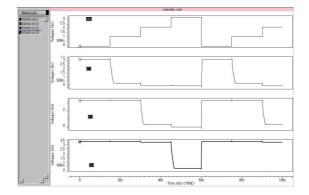

#### 2.2 Thermometer code output circuit

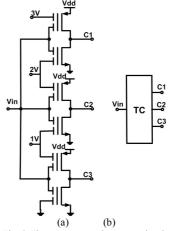

Figure 3 is the thermometer code output circuit made up of 3 DLCs. Threshold voltage  $V_{TH}$  is 2.5, 1.5, and 0.5, respectively from the top DLC in Figure 3. It outputs binary thermometer code according to the input value of  $V_{in}$ . Table 2 simplifies the relationship between the input and the output of thermometer code circuit, and Figure 4 shows the result waveform of the simulation experiment of thermometer code circuit.

Fig. 3 Thermometer code output circuit. (a) Circuit.(b) Symbol.

Table 2: Input and output of thermometer code output circuit

|                      | $C_1$ | $C_2$ | $C_3$ |

|----------------------|-------|-------|-------|

| V <sub>0</sub> (GND) | 3     | 3     | 3     |

| $V_1$                | 0     | 3     | 3     |

| $V_2$                | 0     | 0     | 3     |

| V <sub>3</sub> (VDD) | 0     | 0     | 0     |

Fig. 4 Input and output waves of thermometer code circuit.

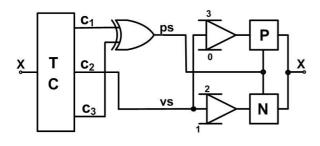

## 2.3 Quaternary identity logic circuit

Quaternary identity logic circuit works as a buffer and is used in designing quaternary D flip-flop. As shown in Figure 5. Quaternary identity logic circuit is composed of thermometer code circuit, EXOR gate, 2 bias inverters, Ntype transmission gate, and P-type transmission gate. When quaternary logic data is entered to input x of quaternary identity logic circuit, thermometer code value is yielded as the thermometer code circuit, C<sub>1</sub>, C<sub>2</sub>, C<sub>3</sub>, like table 3. C<sub>1</sub> and C<sub>3</sub> go through EXOR and yields PS and C<sub>2</sub> directly transmits to VS. Bias inverter with bias  $V_H = 3$ ,  $V_L = 0$ , yields 0 for the output when the input is  $V_{in} > 1.5$ , and yields 3 when  $V_{in} < 1.5$ .

Fig. 5 Quaternary identity logic circuit.

Bias inverter with bias  $V_H = 2$ ,  $V_L = 1$ , yields 1 for output when input is  $V_{in} > 1.5$ , and yields 2 when  $V_{in} < 1.5$ . In the transmission gate, when PS value is 3 the input of N-type transmission gate is transmitted to the output, and when 0 the input of P-type transmission gate is transmitted. The logic value of thermometer code output, PS, VS and output  $V_{out}$  according to the quaternary input x, is like it is shown in table 3. Figure 6 shows the result waveform of the simulation experiment of quaternary identity logic circuit.

Table 3: Operation characteristics of quaternary identity logic circuit

| Х | C <sub>1</sub> | $C_2$ | C <sub>3</sub> | VS | PS | Vout |  |

|---|----------------|-------|----------------|----|----|------|--|

| 0 | 3              | 3     | 3              | 3  | 0  | 0    |  |

| 1 | 0              | 3     | 3              | 3  | 3  | 1    |  |

| 2 | 0              | 0     | 3              | 0  | 3  | 2    |  |

| 3 | 0              | 0     | 0              | 0  | 0  | 3    |  |

|   |                |       |                |    |    |      |  |

Fig. 6 Quaternary input and output waves of identity logic circuit.

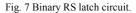

#### 2.4 Binary RS latch circuit

When quaternary Q-IDEN D flip-flop is designed, binary acting RS latch circuit is used to give additional function of flip-flop to quaternary identity logic circuit. The circuit shown in figure 7 is a binary latch circuit using general MOSFETs. The binary latch circuit of figure 7 is a circuit that when CLK input is 3V, output V<sub>out</sub> is determined by R, S input. Table 4 shows the truth table of RS latch circuit and Fig. 8 shows the result waveform of the simulation experiment of RS latch circuit.

|   | Table 4: Truth table of RS latch circuit |                     |                  |  |  |  |  |  |  |  |

|---|------------------------------------------|---------------------|------------------|--|--|--|--|--|--|--|

| S | R                                        | Q                   | Q_bar            |  |  |  |  |  |  |  |

| 0 | 0                                        | status<br>unchanged | status unchanged |  |  |  |  |  |  |  |

| 0 | 3                                        | 0                   | 3                |  |  |  |  |  |  |  |

| 3 | 0                                        | 3                   | 0                |  |  |  |  |  |  |  |

| 3 | 3                                        | unusable            | unusable         |  |  |  |  |  |  |  |

Fig. 8 Input and output waves of RS latch circuit.

# 3. Designing Q-IDEN D flip-flop

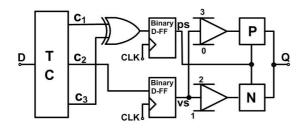

As shown in figure 9. Q-IDEN D flip-flop is composed of binary D flip-flop and multi-valued Identity logic circuit. According to quaternary D input, thermometer code output circuit yields C1, C2 and C3 after converting them to thermometer code, like it is shown in figure 9.

Fig. 9 Q-IDEN D flip-flop.

Table 5: Operation characteristics of Q-IDEN D flip-flop

| D | $C_1$ | $C_2$ | $C_3$ | BD1 | BD2 | VS | PS | Q |

|---|-------|-------|-------|-----|-----|----|----|---|

| 0 | 3     | 3     | 3     | 0   | 3   | 3  | 0  | 0 |

| 1 | 0     | 3     | 3     | 3   | 3   | 3  | 3  | 1 |

| 2 | 0     | 0     | 3     | 3   | 0   | 0  | 3  | 2 |

| 3 | 0     | 0     | 0     | 0   | 0   | 0  | 0  | 3 |

The result of C<sub>1</sub> and C<sub>3</sub> gone through EXOR becomes the input of upper binary D flip-flop and get stored as PS. C<sub>2</sub> becomes the input of lower binary D flip-flop and get stored as VS. By using binary flip-flop, total circuit obtains the function of the flip-flop. Bias inverter with  $V_{\rm H}$  = 3,  $V_{\rm L}$ = 0, yields 0 for output when input is  $V_{in} > 1.5$ , and yields 3 when  $V_{in} < 1.5$ . Bias inverter with  $V_H = 2$ ,  $V_L = 1$ , yields 1 for output when input is  $V_{in} > 1.5$ , and yields 2 when  $V_{in} < 1.5$ . When PS value is 3 the input of N-type transmission gate is transmitted to the output, and when 0 the input of P-type transmission gate is transmitted. Eventually, the logic value of output Q and input D become identical. Table 3.12 shows the logic value of thermometer code, PS, VS, and output Q according to input D. Figure 10 shows the result waveform of the simulation experiment of Q-IDEN D flip-flop.

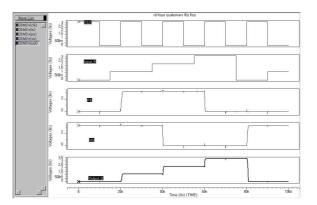

Fig. 10 Quaternary input and output waves of Q-IDEN D flip-flop.

# 4. Comparision and Discussion

In this chapter, we verified the action condition of quaternary Q-IDEN D flip-flop through HSPICE simulation experiment on 0.35  $\mu$ m 1-poly 6-metal CMOS process. The Q-IDEN D flip-flop suggested in this report was compared with previously reported multi-valued Flip-flop in the aspect of propagation delay characteristics and power consumption, and it is summarized in table 6. Supply voltage was 3.3V and the logic level 0, 1, 2, and 3 of input and output was 0.0V, 1.1V, 2.2V, and 3.3V, respectively.

| Flip-Flop | Author         | Γ<br>(μm) | S.V.<br>(V) | Propagation<br>Delay(ns)/P <sub>D</sub> |

|-----------|----------------|-----------|-------------|-----------------------------------------|

|           | Elgamel[5]     | 0.18      | 3.3         | 0.224/19.8 µW                           |

| Binary    | Do[6]          | 0.18      | 1.8         | 0.138/4.7 mW                            |

| Flip-Flop | Sung[7]        | 0.18      | 1.5         | $0.402/47.8~\mu W$                      |

|           | Shin[8]        | 0.35      | 3.3         | 0.427/540 µW                            |

|           | Current[3]     | 2         | 5           | 2.8/354.8 µW                            |

| Multi-    | Inaba(I)[4]    | 0.6       | 3.5         | 420/80 µW                               |

| valued    | Inaba(II)[4]   | 0.6       | 3.5         | 130/155 μW                              |

| Flip-Flop | Q-IDEN<br>D_FF | 0.35      | 3.3         | 0.43/138 JM                             |

Table 6: Comparison of the propagation delay characteristics

Among the characteristics of binary flip-flop, the power consumption of Do was 4.7 mW. This is very much for the power consumption of binary flip-flop. In case of Elgamel, Sung, and Shin it was detected in  $\mu$ W s.

Current suggested quaternary latch circuit using binary CMOS RS latch and proved that propagation delay characteristics was 2.8 ns when power consumption was  $354.8 \mu$ .

Inaba designed multi-valued using Neuron-MOS, suggested D flip-flop, and proved that in analog D flip-flop propagation delay characteristics was 420 ns when power consumption was  $80 \,\mu$  and in quantize D flip-flop 130 ns when 155  $\mu$ .

Propagation delay characteristics of the Q-IDEN D flipflop, suggested in this report, was 0.43 ns when power consumption was 138  $\mu$ , and it is similar to the propagation delay characteristics of the binary flip-flop.

# 5. Conclusion

In this study, we suggested and designed Q-IDEN D flipflop. Suggested Q-IDEN D flip-flop was designed using bias inverter, transmission gate, thermometer code output circuit, and binary RS latch circuit.

Q-IDEN D flip-flop showed 138 / W of power consumption, 0.43 ns of propagation delay, and 59.3fJ of PDP, the better characteristics than previous flip-flops.

The problems occurred during the study, excessive power consumption of Neuron-MOS device circuit and raising the max-sampling frequency, are still remained to be investigated in the future.

## References

[1] T. Shibata and T. Ohmi, "A Functional MOS TransistorFeaturing Gate-Level Weighted Sum and Threshold Operations," *IEEE Trans. Electron Device*, vol. 39, no. 6, June 1992.

[2] K. W. Current, "Design of a Quaternary Latch Circuit Using a Binary CMOS RS Latch," *Proc. 30th ISMVL*, pp. 377-381, May 2000.

[3] T. Uemura, and T. Baba, "A Three-valued D-Flip-Flop and Shift Register using Multi-Junction SurfaceTunnel Transistors," *Proc. 31th ISMVL*, pp. 89-93, May 2001.

[4] M. Inaba, K. Tanno, and O. Ishizuka, "Multi-Valued Flip-Flop with Neuron-CMOS NMIN Cricuits," *Proc. 32nd ISMVL*, pp. 282-288, May 2002.

[5] M. Elgamel, T. Darwish, M. Bayoumi, "Noise Tolerant LowPower Dynamic TSPCL D Flip-Flops, "Proc. IEEE CSAS 2002,pp.80-85, Apr.2002.

[6] M.A. Do, X.P. Yu, J.G. Ma, K.S. Yeo, R. Wu, Q.X. Zhang, "A 2GHz Programable Counter with New re-loadable D flipflop," Conf. IEEE Electron Devices & Solid-state Circuits. 2003, pp. 269-272, Dec. 2003.

[7] Y.Y. Sung, R.C. Chang, "A Novel CMOS Doubleedge Triggered Flip-Flop for Low-Power Applications," *Proc. IEEE ISCAS 2004*, pp. 665-668, May 2004.

[8] S.D. Shin, B.S. Kong, "Variable Sampling Window Flip-Flops for Low-Power High-Speed VLSI," *Proc. IEE Devices & Systems*, pp. 266-271, June 2005.

**Sang mi Shim** received the B.S. degree in Computer Engineering from Konyang University, Daejeon, Korea, in 1996. and the M.S. degree in Electronic Engineering from School of Electronic Engineering from Inha University, Incheon, Korea, in 1999. She has been received the Ph.D.

course in Electronic Engineering at the School of Electronic Engineering from Inha University, Incheon, Korea from 2001. Her main research interests are in the areas of biomedical signal processing, healthcare system and various industrial applications.

**Gi Soo Na** received the M.S. and Ph.D degrees in Electronic Engineering

from inha University in 1999 and 2005, respectively.

From 2001 to 2005, he was a lecture in the Department of Electronics Engineering, Korea Polytechnic University. He has taught courses in analog signal processing

and analog circuit . He is currently a Research Professor with the Information, Communications & Electronics Engineering catholic University of korea. His research activities are mainly in the areas of analog processing, integrated circuit system, analog system.

**Seung woo Park** received the B.S. degree in Electronic Engineering from Honam University, Gwangju, Korea, in 2002. and the M.S. degree in Electronic Engineering from School of Electronic Engineering from Inha University, Incheon, Korea in 2004. He has been

received the Ph.D. course in Electronic Engineering at the School of Electronic Engineering from Inha University, Incheon, Korea from 2004. His main research interests are in the areas of medical image processing, radiation instrument and biomedical signal processing.

**Seung hong Hong** received the B.S. degree in Electrical Engineering from Inha University in 1963. He received the M.S. degree in Electrical Engineering from Inha University in 1966, and the Ph.D. degree at the School of Biomedical Engineering from Tokyo University, Japan in 1975,

respectively. He was a director and chairman at the Institute of Electronic Engineer of Korea from 1981 to 1994. He was a director, vice chairman, and chairman at the IEEE Korea Section from 1983 to 1997. He has been with the Department of Electronics Engineering at In-ha University. His main research interests are in the areas of bio-signal processing, rehabilitation engineering, medical image processing.