# FPGA Based Speed Control of AC Servomotor Using Sinusoidal PWM

Kariyappa B. S<sup>1</sup> Dr. M. Uttara Kumari<sup>2</sup>

<sup>1</sup>Professor, ECE Department, R V College of Engineering, Bangalore-59, India <sup>2</sup>Asst. Professor, ECE Department, R V College of Engineering, Bangalore-59, India

### Abstract

This paper presents a Xilinx Field Programmable Gate Array (FPGA) based speed control of AC Servomotor using sinusoidal PWM technique. Xilinx FPGA is a programmable logic device developed by Xilinx which is considered as an efficient hardware for rapid prototyping. It is used to generate 50 Hz sine wave, the triangular wave and the sinusoidal PWM signals. The sinusoidal pulse width controls the speed of Motor. The proposed control scheme has been realized using Xilinx FPGA SPARTAN XC3S400 and tested using SM115 model Alternating Current (AC) servomotor. The result provides a controllable speed with satisfactory dynamic and static performances.

## Keywords:

Sinusoidal Pulse Width Modulation (SPWM), Field Programmable Gate Array (FPGA), Insulated Gate Bipolar Transistor (IGBT)

# **1. Introduction**

Pulse Width Modulation is widely used in power electronics as a controller in power conversion and motion control. Among different types of modulating modes the Sinusoidal PWM and Space Vector PWM are two common strategies in adjustable speed drive system. The Pulse width of SPWM varies with the Sine wave so as to restrain the lower order harmonics with easy control and large D C utilization [1].

With successively improving reliability and performance of digital controllers, the digital control techniques have predominated over other analog counter parts.

The advantages of digital controllers are:

- 1 Reconfigurability

- 2 Power saving options

- 3 Less external passive components

- 4 Less sensitive to temperature variation

Micro-processor based digital control schemes have been applied to the close loop regulation of PWM inverters. Micro-processor based control schemes[2] have the advantage of flexibility, higher reliability and lower cost, but the demanding control requirements of modern power conditioning systems will overload most of the general purpose micro-processors and the computing speed of microprocessor limits the use of microprocessor in complex algorithms.

Digital Signal Processors (DSPs) [3] and Microcontrollers [4] are used for digital control applications. But DSPs and Microcontrollers can no longer keep pace with the new generation of applications that requires higher performance and more flexible without increasing cost and resources.

Further microprocessors, Microcontrollers and DSPs are sequential machines that mean tasks are executed sequentially which takes longer processing time to accomplish the same task.

The high speed hard wired logic can enhance the computation capability. The ASIC based technology provides a rapid and low cost solution for special applications with large market. Owing to the progress of technology, the life cycle of most modern electronic products become shorter than their design cycle. The emergence of FPGA has drawn much attention due to its shorter design cycle, lower cost and higher density. The simplicity and programmability of FPGA make it the most favorable choice for prototyping digital systems. When comparing the dynamic performance and control capabilities in PWM controlled Power converters FPGA-based digital techniques are better than DSPs[5].

## 2. Principle of Generating SPWM

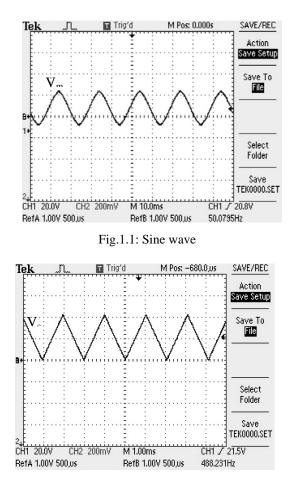

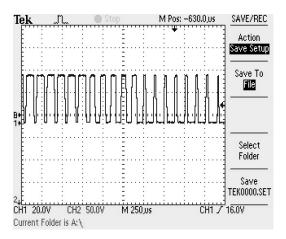

The Sine Wave is used as a reference to generate PWM, because many AC Motors runs at 50 Hz supply, the 50 Hz Sine Wave( $V_m$ ) is generated using FPGA controller as shown in figure1.1. The high frequency Triangular wave( $V_c$ ) shown in figure1.2 is used as a carrier signal. This high frequency Triangular wave carrier signal is compared with a Sinusoidal reference signal. The crossover points are used to determine the switching instants such that if  $V_{reference}$  is greater than  $V_{carrier}$  then output is high otherwise output is low. The SPWM output is shown in figure1.3

Manuscript received October 5, 2008

Manuscript revised October 20, 2008

Fig.1.2: Triangular wave

Fig.1.3: SPWM wave

## 3. System Overview

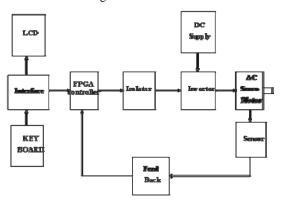

The proposed system consists of FPGA Controller for generating SPWM signals, keyboard to enter required speed, LCD to display speed of Motor, isolator for protection, inverter to convert DC to AC, the feedback system and Motor. The Block diagram of the proposed system is shown in figure2.

Fig.2: proposed Block diagram

The 4X4 keyboard is interfaced to FPGA controller, it accepts 4 digit decimal numbers as speed. The 16X2 LCD is used to display the entered speed and the actual speed of the motor.

The Isolation circuit provides electrical isolation between FPGA controller and PWM inverter. FPGA operates at 5V, it is desired to isolate the control board from higher voltage of the Inverter circuit. It is also used to increase the input signal voltage to the required level of gate signal.

### 3.1. FPGA Controller

FPGA Controller generates 50 Hz Sine wave and high frequency carrier wave. The carrier signal is compared with the reference Sine wave to generate SPWM signals. An external main clock is used as a clock signal to the Xilinx FPGA in order to get the 50 Hz sine wave and carrier frequency. At every reference line crossing of Sine wave the signals are separated to obtain gate1 and gate2 signals.

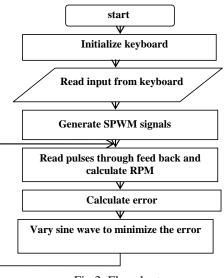

FPGA controller also compares the entered speed and the Motor speed from feedback, based on the difference, the width of SPWM is varied by varying sine wave. The flowchart of the FPGA controller is shown in figure3.

Fig.3: Flowchart

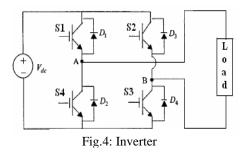

#### **3.2. PWM Inverter**

The basic full bridge Insulated Gate Bipolar Transistor (IGBT) based inverter is shown in figure4, it converts DC to AC. The Inverter has a simple circuit topology and fewer components which lead to low cost and high efficiency. The two gate signals from the FPGA controller are applied to gate input of PWM inverter through isolator. The gate1 signal (i.e. SPWM from first half cycle of sine wave) is given to s1, s3 switches and gate2 Signal (i.e. SPWM from next half cycle of sine wave) is given to s2, s4 switches.

The IR sensor circuit is used to calculate the motor speed. The sensor circuit generates one pulse for each rotation of the motor, these pulses are counted in FPGA controller for one second and multiplied by 60 to get the speed of the motor in rpm. If the entered speed and feedback speed are different, then the amplitude of the sine wave is varied to minimize the difference.

## 4. Results and Conclusion

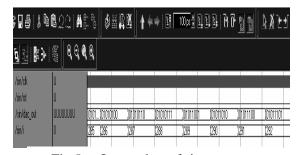

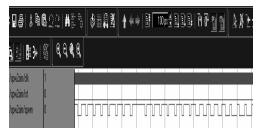

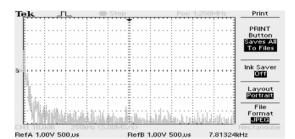

The FPGA based SPWM has been designed using VHDL Programming language. The frequency, amplitude of sine wave and SPWM are verified using Modelsim simulation tool. The simulated outputs are shown in figure5a and 5b. This code is downloaded into XILINX SPARTAN 3 XC3S400 FPGA Board, the results are tested using TEKTRONIX CRO and are shown in figure6. The FFT output of SPWM is shown in figure7.

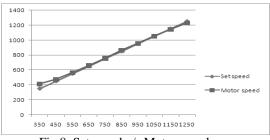

The design of switching pulses using FPGA controller shall produce better control signals for inverter switches. This hardware is tested by running AC Servo Motor SM115 model at different speeds. The figure8 shows variation of set speed v/s Motor speed. The result shows higher efficiency in achieving the set speed. The experimental setup is shown in figure9. The performance can be further improved by using LC filter which reduces the higher harmonics.

Fig.5.a: Output data of sine wave

Fig.5.b: Output waveform of SPWM

Fig.6: Gate1, gate2 Wave forms

Fig.7: FFT output of SPWM

Fig.8: Set speed v/s Motor speed

Fig.9: Experimental setup

## **References:**

- Bai Hua,Zhao Zhengming, Meng shuo,Liu Jianzheng, Sun xiaoying, "Comparison of Three PWM strategies—SPWM,SVPWM and one cycle control" IEEE 0-7803-7885-7/03, 2003.

- [2] B. N. Mwinyiwiwa, Z.Wolanski, and B. T. Ooi, "Microp- rocessor implemented SPWM for multiconverters with phase-shifted triangle carriers" IEEE-IAS Annu. Meeting, NewOrleans, pp. 1542-1549, Oct. 1997.

- [3] Kay soon low "A DSP-based Single-Phase AC Power source" IEEE trans on industrial electronics vol-46,no.-5,OCT-1999.

- [4] Caurentiu Dimitriu, Mihai luconu, C Aghion, Ovidiu Ursaru "Control with microcontroller for PWM single phase inverter": IEEE 0-7803-7979-9/03 © 2003.

- [5] A. Fratta, G.Griffero and S. Nieddu, "Comparative Analysis among DSP and FPGA-based Control Capabilities in PWM Power Converters", the 30th Annual Conference of the IEEE Industrial Electronics Society, Nov. 2004.

- [6] E. Monmasson, Y.A. Chapuis, "Contributions of FPGAs to the Control of Electrical Systems, a Review" IES News letter, Vol. 49, no.4, 2002.

Dr. M.Uttara Kumari, Professor in the Department of Electronics & Communication RV at College of Engineering, Bangalore, India. She is P.G Co-Ordinator for VLSI and Embedded Systems. She has obtained her doctoral degree

for thesis on Signal Modeling for Sidelobe reduction in Pulse Compression Radar from Andhra University, Vishakhapatnam. She obtained her Masters degree in Electronics from Bangalore University and BE degree in Electronics & Communication Engineering from Nagarjuna University, Guntur. Her research interest are Signal Processing, Adaptive signal processing. She is a member of ISTE, IETE. She has published papers at various journals and International conference. Presently she is guiding 3 P.hd students.

#### Mr.B.S.Kariyappa,

Assistant Professor in the Department of Electronics & Communication Engineering at RV College of Engineering, Bangalore, India. He is pursuing his PhD in the field of power Controllers. He obtained his

Masters degree in Electronics & Communication Engineering from Bangalore University and BE in Electronics & Communication Engineering from Bangalore University. His research interests are VLSI & VHDL and power controllers. He has published papers at various journals and International conference. He is a member of ISTE, IETE.